7nmプロセスで360平方mmの大型ダイ

Microsoftの次世代ゲーム機「Xbox Series X」は、AMDのZen 2系CPUコアとRDNA系GPUコアをベースとしたカスタムSoCを心臓として備える。

アーキテクチャの系列としては、前世代同様にPlayStation 5(PS5)と近似性がある。Microsoftは、アーキテクチャを積極的に公開しており、今年(2020年)8月に開催されたプロセッサカンファレンスのHot Chipsで、アーキテクチャ概要が明らかにされた。

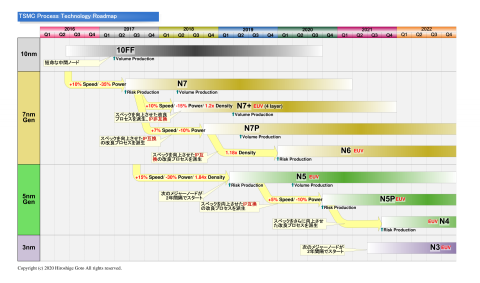

Xbox Series XはTSMCの7nmノードプロセスの「N7」の拡張版「N7e」で製造される。ダイは360.4平方mmで、153億トランジスタ。そのなかでGPUコアが最大の面積を取っている。

Xbox Series XのGPUコアは、AMDの「RDNA 2」アーキテクチャと機能はよく似ている。RDNAをベースに、レイトレーシング(Ray Tracing)のハードウェアアクセラレーションと、バリヤブルレイトシェーディング(Variable-Rate Shading:VRS)やサンプラフィードバックストリーミング(Sampler Feedback Streaming:SFS)などの制御機能を備える。

AMD系のGPUコアは、「CU(Compute Unit)」と呼ばれる演算ユニットを基本構造としている。Xbox Series XのGPUコアはトータルで52個のCUを備える。各CUには64個のFP32積和算コア(Streaming Processor)が搭載されており、トータルでは3,328個の積和算ユニットとなる。動作周波数は1.825GHzであるため、ピーク性能は12TFLOPSにのぼる。

ベースはAMDのRDNA系アーキテクチャ

Xbox Series XのGPUのアーキテクチャは、AMDのRDNA系アーキテクチャをベースにしている。基本的な構造はRDNAと同じだ。CUにはグラフィックスの演算とテクスチャなどの基本的なプロセッシングユニットがすべて含まれる。

第1世代のRDNAとXbox Series Xの設計でもっとも大きな部分は、レイトレーシングのアクセラレータユニット「レイアクセラレータ(Ray Accelerator)」の搭載だ。レイアクセラレータは、各CUに1ユニットずつ搭載されている。

基本構造から見ると、AMDのRDNAアーキテクチャでは、2個のCUが結合した構造となっている。2個のCUで構成されるユニットは、「WGP(Workgroup Processor)」と呼ばれる。

WGPには、2個のCUのほかに、命令キャッシュ、スカラデータキャッシュ、ローカルのスクラッチパッドメモリである「ローカルデータシェアメモリ(Local Data Share Memory:LDS)」が含まれる。これらのユニットは2個のCUで共有されている。WGPが、AMDのGPUの演算クラスタを構成する最小単位だ。

WGP内でのユニットの共有には意味がある。AMDのGPUの実行バッチは「Wavefront」または「Wave」と呼ばれる。そして、Wavefrontをグループ化した「ワークグループ(Workgroup)」単位でプロセッサクラスタであるCUに割り当てられる。

ワークグループは、LDSを使ったデータ共有が可能なグループである。RDNAアーキテクチャでは、ワークグループをCUに割り当てるモードだけでなく、WGPに割り当てるモードも備えている。WGPにワークグループを割り当てる場合は共有のLDSを介して、2個のCUに割り当てられたすべてのWaveでデータ交換ができる。WGP構成を取ることで、より大きなワークグループのなかでのデータ共有を可能にしている。

AMDアーキテクチャのGPUコアのなかでは、WGPは複数ユニットでクラスタを形成している。そして、クラスタ内のWGP間でL1データキャッシュやラスタライザ、プリミティブアッセンブリユニットを共有している。

WGPの内部のCUをさらに分解すると、CUがさらに2個の演算ブロックに分かれている。2個の演算ブロックには、それぞれ命令ユニットがあり、同サイクルに、2命令ユニットがそれぞれが独立して異なる命令ストリームの命令を実行ユニット群に対して発行できる。

CU内の実行ユニット群は、2組の演算ブロックに分かれているユニットと、共有のユニットがある。32レーンのベクタ演算ユニット(VALU)と1個のスカラ演算ユニット(SALU)、メッセージングなどの制御系のユニットは、2セットずつ備えられている。

2個の命令ユニットは、それぞれ専用のVALUとSALUと制御ユニットに命令を発行する。一方、メモリアクセス系のユニットは、1ユニットを2つの演算ブロックで共有するユニット群となっている。CU内の共有リソースには、ロード/ストア、テクスチャプロセッシング、ローカルデータシェアアクセスが含まれている。

2個の命令ユニットから2セットの演算アレイと共有リソースに命令発行

Xbox XのGPUコアのCUには、レイトレーシングのアクセラレータユニット「レイアクセラレータ(Ray Accelerator)」が実装されている。レイアクセラレータは、各CUに1ユニットで、2つの命令ユニットの共有リソースとなっている。

この点は、テクスチャユニットと同じだ。CU内のレイアクセラレータは、4レイオペレーションを1クロックで実行と説明されている。

通常、レイトレーシングのアクセラレーションでは、レイトレーシングのフローのなかで、レイを伸ばす「トラバーサル(Traversal)」とレイとオブジェクトの交差を判定する「インターセクションテスト(Intersection Test)」をハードウェアで処理する。

1つのレイのトレーシングには複数オペレーションが必要と見られるため、4レイオペレーション/クロックは、そのままレイ処理性能に置き換えられるわけではない。

レイトレーシングのスペックとしては、GPUコア全体でピークで380G/sレイボックス、95G/sレイトライアングル。Microsoftは、シェーダプロセッサ上のソフトウェアでレイトレーシングを実行する場合と比べて、最大10倍の性能と説明している。

AMDのRDNA CUでは、2個の命令ユニットは、それぞれが1個のベクタALU命令と1個のスカラALU命令、そして1個の制御命令、1個のベクタデータ命令を同時に発行できる。最大で4命令/サイクルだ。

Microsoftは今回、CU内部では合計で7命令を同時に発行可能と説明している。2個のベクタALU命令、2個のスカラALU命令、2個の制御命令、そして1個のベクタデータ命令だ。

ベクタデータ命令だけは1命令/サイクルとなっている。ベクタデータ命令の実行ユニットは共有ユニットであるため、命令のアービターが2つの命令ユニットからの命令を調停する。そのため、ベクタデータ命令は、各サイクルに1命令と見られる。

じつは、AMD RDNAの場合、共有リソースで実行される命令はベクタメモリ命令、テクスチャ命令、ローカルデータシェア(LDS)命令があり、Xbox Series Xではさらにレイトレーシング命令もある。

Microsoftの説明からすると、これらのユニット群に対する命令は、各サイクルに1命令だと見られる。つまり、共有のアービターユニットがあり、2個の命令ユニットからのベクタメモリ/テクスチャ/LDS/レイトレーシング命令が調停されて各サイクル1命令が発行されると推測される。

共有リソースとして分離されたレイアクセラレータ

GPUの場合、演算系命令のスケジューリングとメモリアクセスが伴う命令のスケジューリングが明確に分離されているケースが多い。GPUの場合、インフライトで扱うスレッド数が多いため、演算命令は決め打ちのレイテンシで、スレッドを切り替えることでレイテンシを隠蔽できる。

しかし、レイテンシが不定で長いメモリアクセスの場合は、異なる制御が必要となる。そのため、分離して制御することが理にかなう。レイアクセラレータも、3D空間のオブジェクトを階層管理するバウンディングボリューム(BVH)データにアクセスする必要があり、レイテンシが不定のオペレーションとなると見られる。

Xbox Series Xでのレイアクセラレータの実装方法は、NVIDIAではじめてレイアクセラレータを実装したTuringアーキテクチャとある程度似ている。Turingアーキテクチャでは、1個のSM(Streaming Multiprocessor)のなかに4個のプロセッシングブロックがある。命令ユニットと演算エンジン群はそれぞれのプロセッシングブロックに配置され、テクスチャユニットとレイアクセラレータの「RTコア」は共有リソースとなっている。

Xbox Series Xでは2個のブロックがレイトレーシングユニットを共有するのに、Turingは4個のプロセッシングブロックで共有する仕組みだ。しかし、AMDアーキテクチャでは、各演算ブロックのベクタエンジンはFP32で32-way、それに対してTuringでは各プロセッシングブロックのベクタエンジンが16-way。ベクタ演算に対するユニットの共有の比率では同等となる。

こうした構造であるため、Xbox Series XではレイトレーシングのBVHトラバーサルなどのタスクは、シェーダプロセッシングとは完全に分離されて行なわれる。言い換えれば、シェーダパフォーマンスを食わない。

PDF版はこちら

ちなみに、RDNAアーキテクチャでは、Waveのバッチは64エレメントのWave64か、32エレメントのWave32の2モードとなっている。従来のAMDアーキテクチャでは64エレメントだったが、RDNAでは粒度の小さな32エレメントのWave32がメインとなっている。

また、Special Function Unit(SFU)も積和算ユニットから分離されて独立した。そのため、ベクタ命令の実行が大きく変わっている。

グラフィックス描画の制御として、Xbox Series Xではバリヤブルレイトシェーディングと、サンプラフィードバックストリーミングなどの制御機能が導入された。前者でシェーダプロセッシングの負荷を減らし、後者でメモリ帯域への圧迫を減らす。

冗長性のために56個のCUが実装されたGPUコア

Xbox Series Xでは、2個のCUを搭載したWGPが7ユニットバンドルされて、1つのシェーダエンジンアレイとなっている。WGP 7ユニットのクラスタには、ラスタライザとレンダーバックエンドが配置されている。

RDNAアーキテクチャでは、GPUは複数のWGPユニットのクラスタを大きな単位として構成されるが、このクラスタには特別な名称がついていない。ここでは、仮にWGPクラスタとしておく。

AMDの従来のGPUでは、WGPクラスタに相当するクラスタには、ジオメトリプロセッシングユニットが付随していた。しかし、RDNAアーキテクチャでは、ジオメトリパイプラインの最後段の「プリミティブアッセンブリユニット(Primitive Assembly Unit)」だけがWGPクラスタ側に配置されている。プリミティブアッセンブリの前のジオメトリプロセッシングは、GPUコア全体で1ユニットにまとめられている。

WGPクラスタは、ジオメトリ処理から後のパイプラインに必要なユニットがすべて備えられているミニGPUとなっている。また、L1データキャッシュも共有されている。

この構成はRDNAアーキテクチャの特徴だ。従来のGPUでは、レンダーバックエンドはプロセッサクラスタとは内部バスで分離され、L2キャッシュに連結されていた。RDNAではレンダーバックエンドはCU群とクラスタになっており、L1キャッシュを共有している。そのため、WGPクラスタとレンダーバックエンドの間で、フルにカラー圧縮技術を使うことができる。

PDF版はこちら

Xbox Series XのGPUコアは4アレイのWGPクラスタに分離されている。各WGPクラスタには7ユニットのWGPが配置されている。トータルでは物理的には28ユニットのWGP、56ユニットのCUが実装されている。

実際の製品では、これらのうち2個のWGP(=4個のCU)が無効にされている。これは、不良箇所のあるCUを無効にすることで、チップ全体の歩留まりを上げるためで、GPUでは一般的に行なわれている。言い換えれば、4個のCUは製品歩留まりのための冗長ユニットとなっている。

Xbox系のシステムに合わせたデュアルコマンドプロセッサ

Xbox Series XのGPUコア全体の構造で、AMD製のGPUコアとの大きな違いは「グラフィックスコマンドプロセッサ(Graphics Command Processor)」を2ユニット持つことだ。グラフィックスコマンドプロセッサは、グラフィックス描画命令のストリームを処理するスカラプロセッサで、GPUを動かすための指揮センターだ。

実態は、RISC(Reduced Instruction Set Computer)型命令セットのマイクロコントローラで、コマンドのストリームのハンドリングのための命令拡張が行なわれている。

Xbox Series Xは、汎用のコマンドプロセッサを2個備えている。「複数のコマンドプロセッサによって、2つのバーチャルマシンにサポートされた2つの完全に独立したコマンドストリームを(同時に)扱うことができる」とMicrosoftは説明している。通常のGPUは、コマンドプロセッサを1ユニットしか備えていない。

じつは、デュアルコマンドプロセッサは、Microsoftにとっては新しいアーキテクチャではない。前世代のXbox One/Xbox One Xから、デュアルコマンドプロセッサ構成を採用していた。

デュアルコマンドプロセッサは、ゲームOSとシステムOSを併存させるMicrosoftゲーム機ならではのアーキテクチャ上の工夫だ。ちなみに、Xbox One/Xbox One Xでは、CPUコアも独自に拡張し、バーチャルマシン切り替えの高速化を図っていた。

PDF版はこちら

AMDアーキテクチャのコマンドプロセッサには、グラフィックスも含めた汎用のコマンドプロセッサ以外に、コンピュート処理専用のサブセットのコマンドプロセッサである「ACE(Asynchronous Compute Engine)」がある。

ACEは、コンピュートタスクをオンメモリで「Asynchronous Compute Queue」としてキューイングしておいてCU群に割り当てる。Xbox Series Xについては、Microsoftは、複数のAsynchronous Compute Queueを扱うことができると説明しており、スライドにはないがACEが搭載されている。

AMDのGCN(Graphics Core Next)以降のGPUアーキテクチャでは、コマンドプロセッサの下に、GPU全体のワークの振り分けを行なう「ワークディストリビュータ(Work Distributor)」がある。Xbox Series Xのダイアグラムにはワークディストリビュータは描かれていないが、この基本構造が変わるとは思われないため、1ユニットのワークディストリビュータがGPU全体のワークの制御を行なっていると見られる。

Xbox Series Xでは、グラフィックスエンジンが1ユニットとなっている。最近の大型GPUは、グラフィックスパイプラインを複数持つアーキテクチャが多かったが、Xbox Series Xは異なる。

しかし、これはXbox Series Xにかぎらず、RDNA系アーキテクチャに共通の特徴だ。RDNAアーキテクチャでは、GPUの規模にかかわらずジオメトリプロセッサはユニファイドとなっている。

ただし、プリミティブアセンブラは、クラスタに振り分けられている。Xbox Series Xの場合は4クラスタで4個のプリミティブアセンブラとなっている。

Xbox Series XのGPUコアは、RDNAアーキテクチャをベースにレイトレーシングハードウェアを加え、プロセッシングとメモリ効率を上げるための仕組みを組み込んだ。現時点では、まだどこまでがAMD GPU共通の機能で、どこがMicrosoft Xbox Series X特有の機能なのかはわからない。AMDのRDNA2アーキテクチャの「Navi 2X」も、レイトレーシングハードウェアとVRSなどが実装されるからだ。

2020-09-30 21:55:00Z

https://news.google.com/__i/rss/rd/articles/CBMiPmh0dHBzOi8vcGMud2F0Y2guaW1wcmVzcy5jby5qcC9kb2NzL2NvbHVtbi9rYWlnYWkvMTI4MDA2OS5odG1s0gFJaHR0cHM6Ly9wYy53YXRjaC5pbXByZXNzLmNvLmpwL2RvY3MvY29sdW1uL2thaWdhaS8xMjgwLzA2OS9hbXAuaW5kZXguaHRtbA?oc=5

No comments:

Post a Comment